针对直流偏移和谐波干扰的单相锁相环

2024-01-21 小九体育nba直播视频

针对电网都会存在的直流偏移和谐波干扰问题,提出一种基于二阶广义积分器锁相环(SOGI-PLL)的改进型锁相环。该方法在前级二阶广义积分器(SOGI)中增加积分支路并且改为固定频率结构,以抑制直流偏移和简化模型推导等方法,指导改进结构设计,确定相应的参数。所提出的改进型单相锁相环技术能有效地消除直流偏移和高频谐波,同时具备良好的动态性能和稳定能力。最后,通过

全球性环境污染以及能源危机问题,极大地推动了新能源分布式发电的发展。伴随着慢慢的变多的以风能和太阳能等新能源为主的发电装置并入电网,对电力系统的并网控制技术提出了更严苛的要求。锁相技术能够实时获取电网基波电压的相位、幅值,在实现安全稳定并网的过程中起着至关重要的作用。其中,锁相环(Phase-Locked Loop, PLL)由鉴相器、环路滤波器和压控振荡器组成,结构相对比较简单、易于实现,在电力系统中得到了广泛应用。

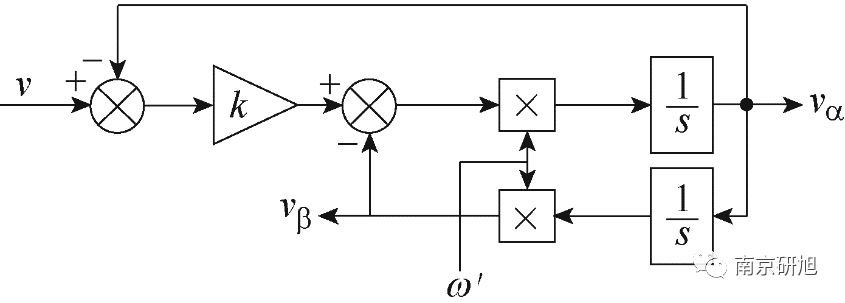

在理想三相并网系统中,使用最多的锁相技术是基于同步旋转坐标系的锁相环(Synchronous Reference Frame-Phase Locked Loop, SRF-PLL),其特点是运用旋转坐标系变换的方法来完成鉴相器的功能,具有动态响应快、软件实现简单的特点。而在单相并网系统中,由于电压相量只有一个,不能直接进行坐标系变换,SRF-PLL实现起来很难。未解决这个问题,通常的做法是利用正交信号发生器(Quadrature Signal Generator, QSG)产生一个与输入电压等幅正交的电压相量,从而完成旋转坐标系变换。二阶广义积分器(SecondOrder Generalized Integrator, SOGI)因为结构相对比较简单、计算量小,具有频率自适应性以及较好的滤波能力,近年来受到众多学者的关注,是构成单相PLL的理想选择。

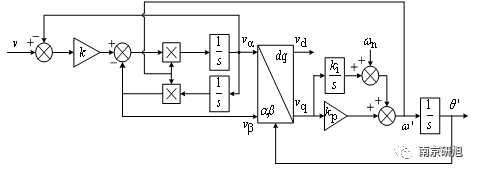

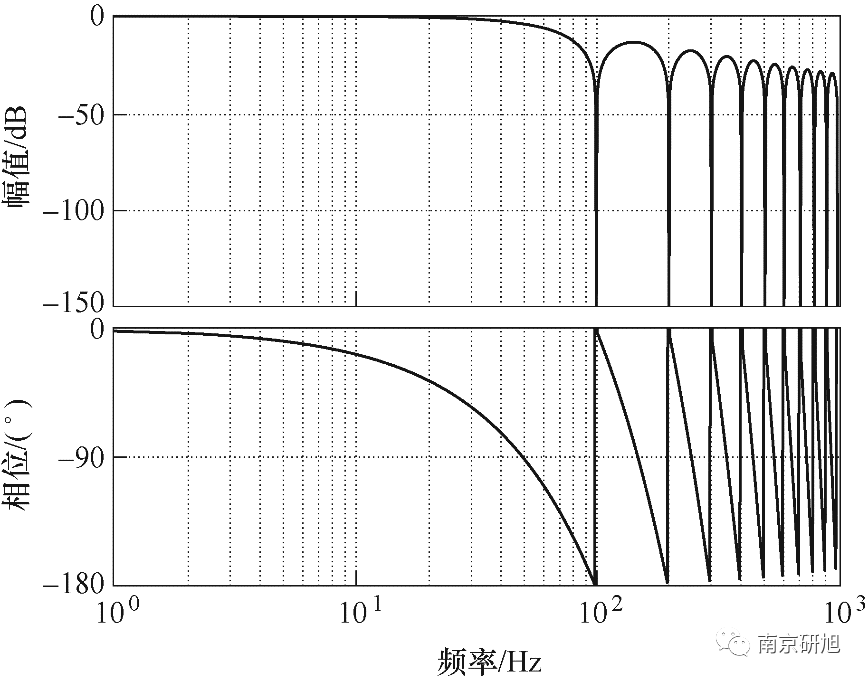

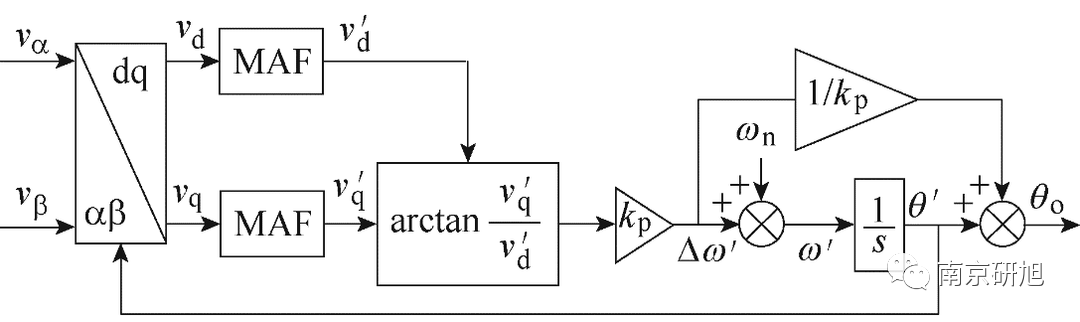

SOGI作为QSG,配合SRF-PLL构成的单相PLL,被大范围的应用于单相并网系统,通常称为SOGI-PLL。SOGI-PLL在理想正弦输入电压的条件下能够准确追踪基波电压相位,但仍存在以下不足:①虽然单相电压不存在基波负序分量,但是传统SOGI不能有效消除电压中的直流偏移,而且对高次谐波的抑制能力不够;②图1中,SOGI-PLL的频率自适应过程是通过SRF-PLL输出的估算频率反馈到SOGI来完成的,增加了控制的复杂性,并且使调谐敏感,以此来降低稳定裕度;③SRF-PLL主要是通过调节PI控制器参数来提高滤波能力,但是带宽必须相应地减小,动态响应变慢。

传统的SOGI结构不能有效消除输入电压中的直流偏移,并且对高次谐波的抑制作用有限。此外,SOGI的传递函数都依赖于中心角频率,一旦输入电压角频率不等于SOGI的中心角频率,SOGI输出的正交信号会存在幅值衰减和相位偏差。因此,为了更好的提高SOGI-PLL在复杂电网环境下的锁相性能,有必要对SOGI的结构可以进行改进和优化。

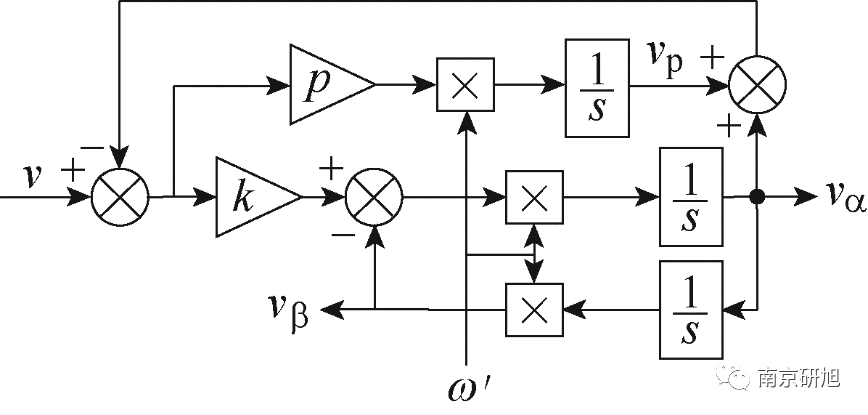

在传统SOGI结构的基础上,通过添加第三个积分器的方式,增强正交信号发生器抑制直流偏移的能力。图3所示的SOGI结构虽然比传统SOGI具有更强的直流偏移抑制能力,但是仍存在一定的缺陷,由于其输出正交信号的传递函数都属于带通滤波器,仍存在依赖于中心角频率的问题,当输入电压发生频率偏移时,会造成输出信号的幅值衰减和相位偏差,在单相锁相环应用场合里,进一步导致估算相位存在稳态误差。

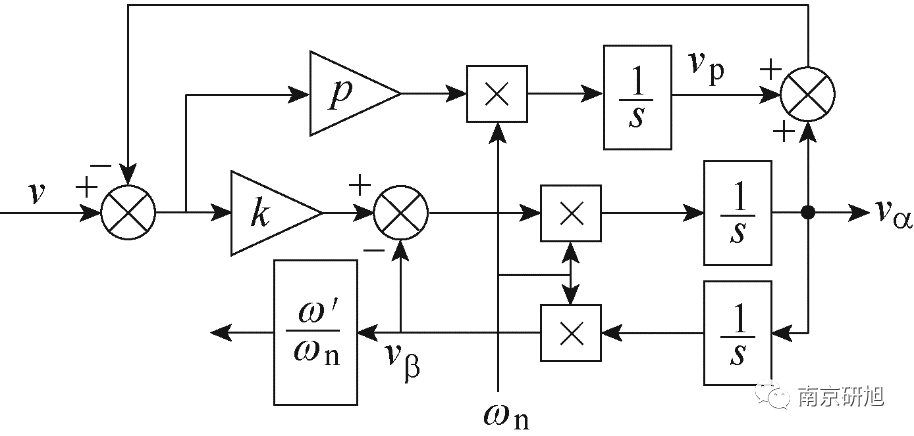

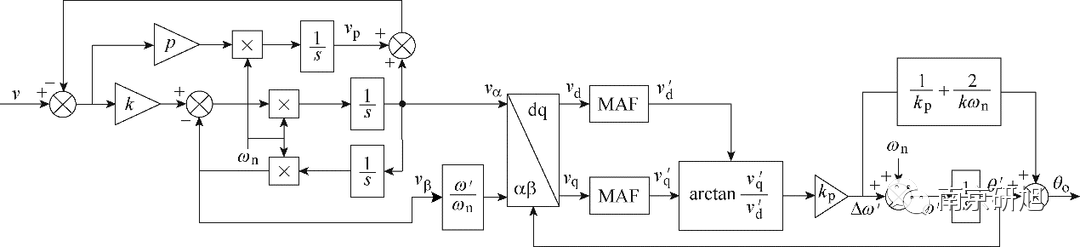

通常情况下,如图1所示的频率自适应结构SOGI-PLL能够解决电网频率偏移带来的问题,然而SOGI和SRF-PLL之间有反馈耦合回路,会增加控制难度和影响系统稳定性。此外,第三条积分支路引入参数p,加大了正交信号发生器参数设计的复杂程度。针对以上问题,本文把可以消除直流偏移的SOGI改成固定频率结构,简称ISOGI,其结构如图4所示。

ISOGI能够有效地抑制输入电压中的直流偏移,然而电网谐波干扰的分布频段很广,ISOGI的滤波能力不足以完全消除。本文在SRF-PLL结构基础上,引入MAF来提升滤波性能,并把PI控制器改成P控制器以加快动态响应速度。

MAF是一种线性相位有限脉冲响应滤波器。显然,MAF具有优越的陷波功能,能够完全滤除频率为1/Tw整数倍的谐波含量。其中,Tw是MAF的窗口宽度。然而,MAF需要一个等于其窗口宽度的等待时间才可以做到稳态,较大的窗口宽度将导致较慢的MAF瞬态响应。针对MAF造成的延时问题,本文把PI控制器换成P控制器以加快系统的响应速度。此外,对q轴电压分量除以d轴电压分量的商进行反正切函数运算,能够消除电压幅值变化对锁相环动态性能和稳定能力的影响,并且使系统线是经过误差补偿之后的改进锁相环(Improve PLL, IPLL)结构。

本文以ISOGI作为正交信号发生器,以IPLL作为锁相结构,提出了一种改进型单相锁相环,简称ISOGI-IPLL,对电网发生频率偏移时ISOGI所造成的滞后相位,在该单相锁相环的估算相位中进行了补偿。

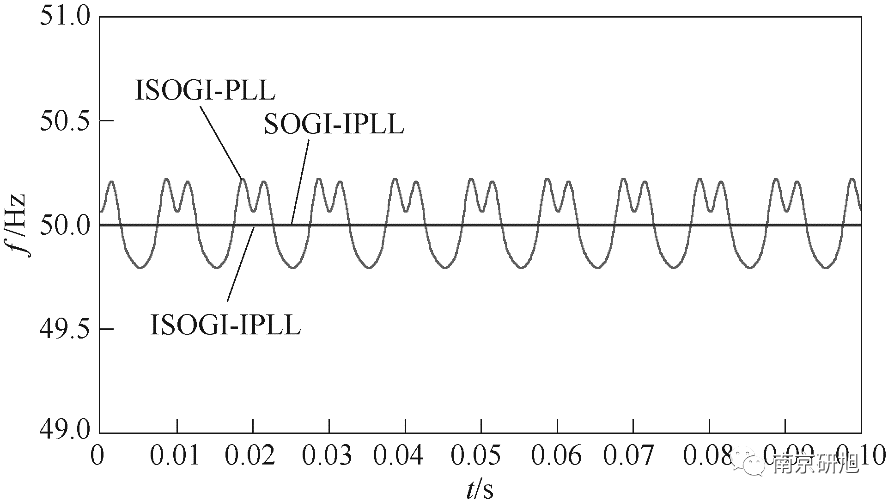

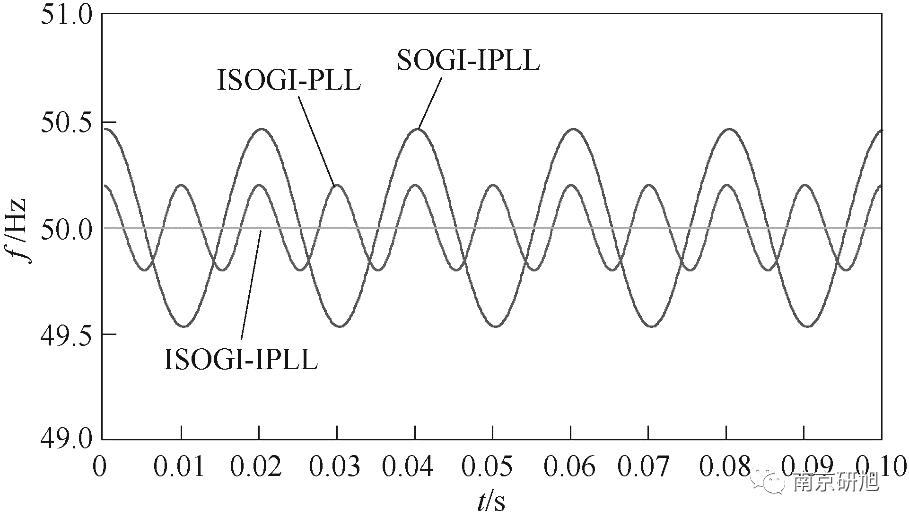

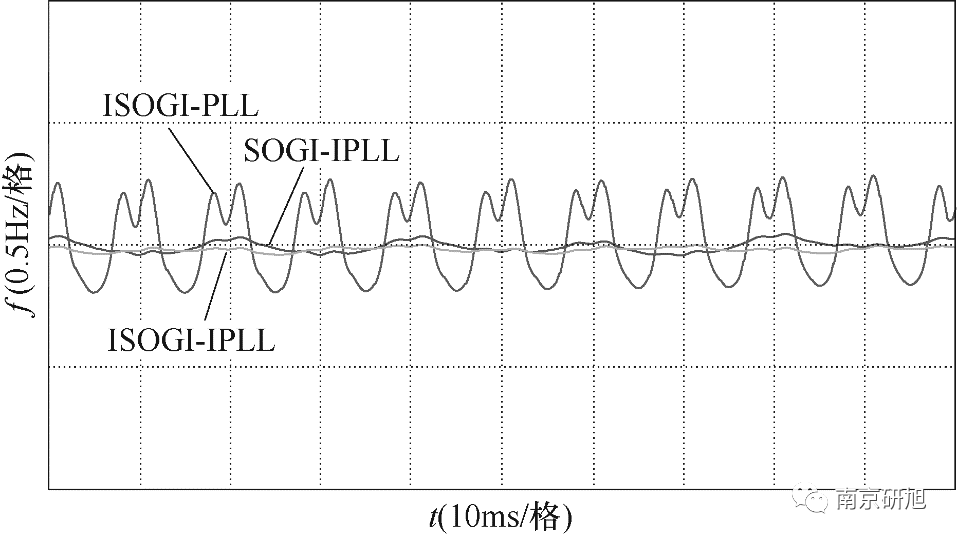

在单相电压中注入0.05pu的-5次谐波和0.05pu的+7次谐波。图8显示了单相锁相环稳态时的估算频率波形。显然,ISOGI-IPLL和SOGI-IPLL都能有效消除谐波分量,实现稳定锁频。但是,ISOGI-PLL受到谐波干扰,输出频率有明显的波动。这说明引入MAF之后,改进锁相结构IPLL的滤波能力得到了极大的提升。

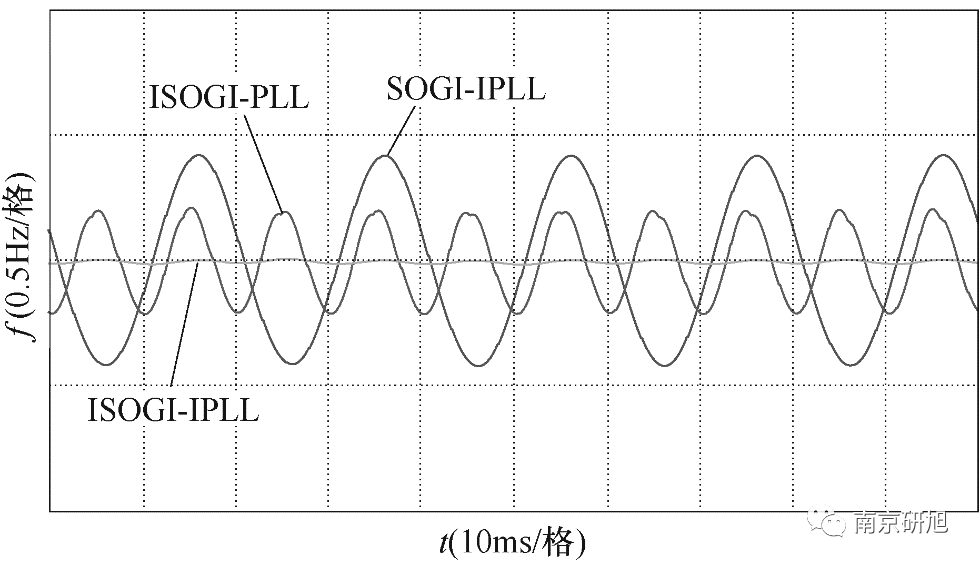

在单相交流电压中注入-20V的直流分量,其仿线所示。显然,直流偏移导致SOGI-IPLL在稳态时存在一倍工频的频率振荡,而ISOGI-IPLL却能够稳定无差锁频,说明ISOGI可以很好地抑制直流偏移。此外,ISOGI-PLL存在二倍工频的频率振荡,从侧面验证了IPLL的滤波能力。

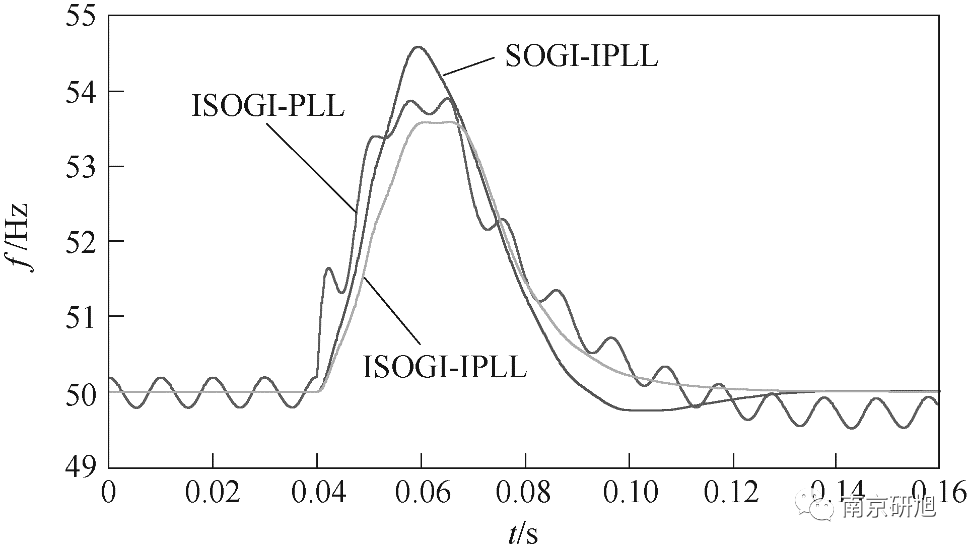

5.3 电网电压相位跳变条件下的仿线°的相位跳变,单相锁相环估算频率的动态响应过程如图10所示。SOGI-IPLL动态过程的超调量大约9.12%;而ISOGI-PLL和ISOGI-IPLL的超调量比较小。ISOGI-PLL需要10个电网周期才能恢复对频率的准确估算,而SOGI-IPLL和ISOGI-IPLL的恢复时间只需5个电网周期。这说明,去掉积分环节之后,IPLL加快了系统的动态响应过程。

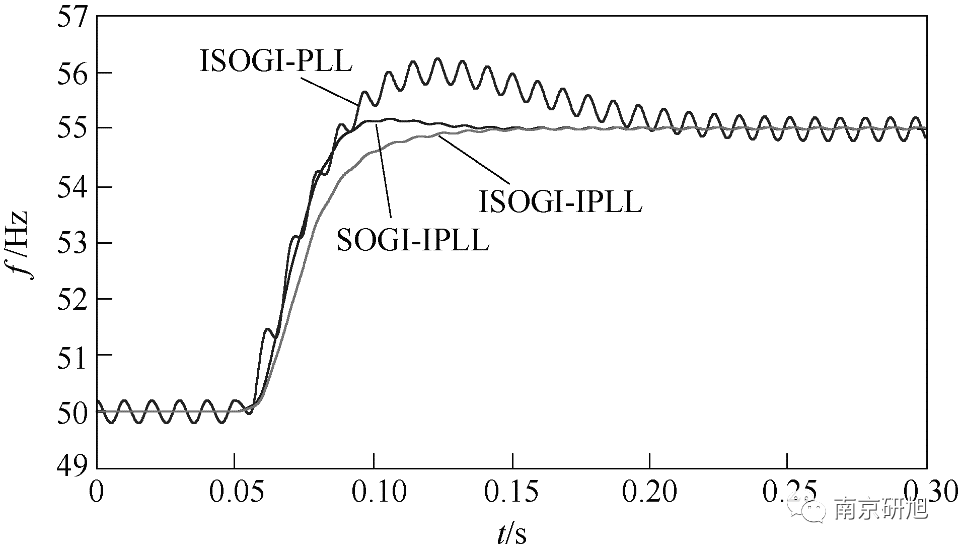

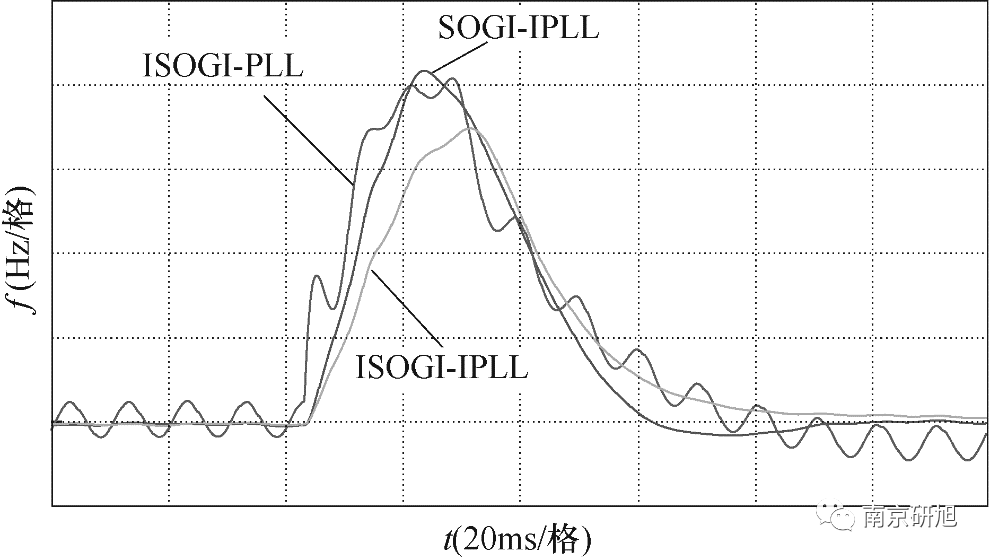

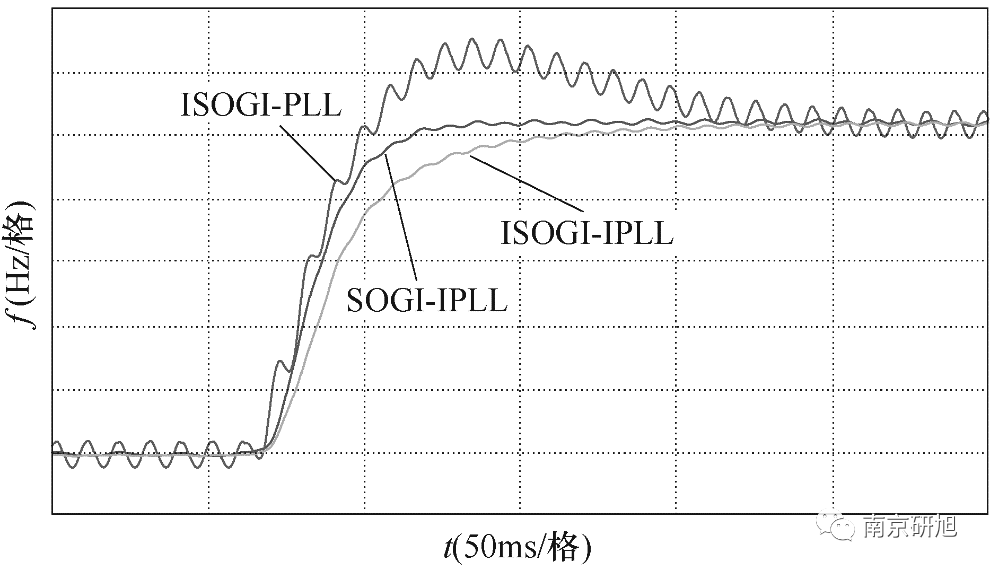

5.4 电网电压频率跳变条件下的仿线s时刻,输入电压发生+5Hz的频率跳变,单相锁相环估算频率的动态响应过程如图11所示。ISOGI-PLL动态过程存在比较大的超调量,约为24%,而SOGI-IPLL和ISOGI-IPLL几乎不存在超调量,动态响应非常平稳,没有稳态误差,证明改进锁相结构IPLL能够很好地解决频率偏移带来的相位偏差问题。同样,ISOGI-PLL需要10个电网周期才能恢复对输入电压的频率追踪,大约是SOGI-IPLL和ISOGI-IPLL所需时间的两倍。因此,本文所提ISOGI-IPLL既能保持很快的动态响应速度,也能减少超调量,来提升了动态性能。

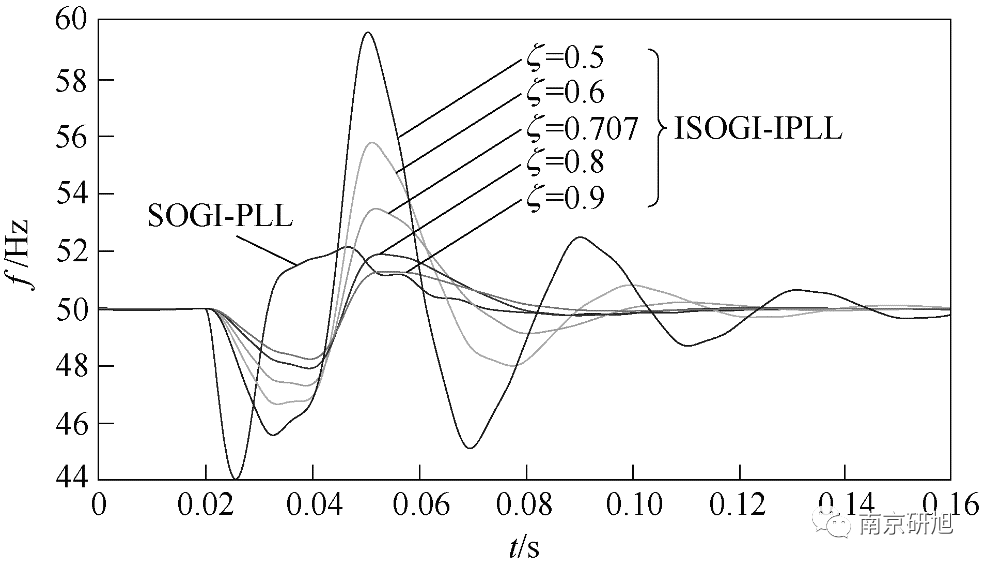

5.5 电网电压暂降条件下的仿线s时刻,输入电压发生-0.5pu的电压暂降,单相锁相环估算频率的动态响应过程如图12所示。传统SOGI-PLL的动态响应过程只有4.34%的超调量和39.2ms的调节时间;而ISOGI-IPLL的动态响应过程受阻尼系数取值的影响。当<0.707时,ISOGI-IPLL的响应曲线存在很明显的振荡现象,并且超调量过大,调节时间太长;当0.707≤≤0.9时,随着的取值逐渐增大,ISOGI-IPLL的超调量从7.62%减小为2.59%,减幅显著,ISOGI-IPLL的调节时间从46.1ms缩短到42.3ms,速度加快;当>0.9时,的数值过大,导致比例系数kp过小,ISOGI-IPLL响应曲线的上升时间太长,当电压频率/相位受到扰动时,锁相系统的追踪速度太慢,影响锁相精度。显然,改进结构在解决直流偏移和高次谐波问题的同时,也对锁相环的整体动态性能造成了一定的影响。由上述分析可知,合理选择的数值,能更加进一步优化ISOGI-IPLL的动态性能。根据实际的需求,的取值可在区间[0.707,0.9]内进行折中选择。

图14表明,相比于传统SRF-PLL,本文提出的IPLL结构具备更强的谐波抑制能力。

图15表明,输入电压含有的直流偏移会导致输出端同时存在单频振荡和倍频振荡。所提ISOGI能抑制直流偏移,有效消除单频振荡分量;所提IPLL能够滤除倍频振荡干扰。

图16表明,当输入电压发生相位跳变时,SOGI-IPLL和ISOGI-IPLL的动态响应过程相似,调节时间比较短,都有平滑的动态响应曲线;然而,ISOGI-PLL受到倍频振荡干扰,响应速度较慢。

图17表明,当输入电压发生频率跳变时,SOGI-IPLL和ISOGI-IPLL的动态响应过程相似,调节时间比较短,都有平滑的动态响应曲线;然而,ISOGI-PLL受到倍频振荡干扰,响应速度较慢。因此,所提IPLL在具有优越滤波功能的同时,兼备良好的动态性能。

针对传统SOGI-PLL的缺陷,本文提出了一种改进单相锁相环技术,适用于电网存在直流偏移和谐波干扰的条件。该方法利用添加积分支路和固定频率结构来改进SOGI,消除直流偏移和优化参数设计;通过引入MAF和去掉积分环节来改进SRF- PLL,抑制高频谐波和加快响应速度。仿真和实验结果一致,验证了理论分析的正确性。实验根据结果得出,改进的单相锁相环技术在直流偏移和谐波干扰的电网故障条件下都能稳定无差地锁定频率,进而准确地追踪电网同步相位,具有响应速度快和鲁棒性强的特点。具体更详细研究内容请参考

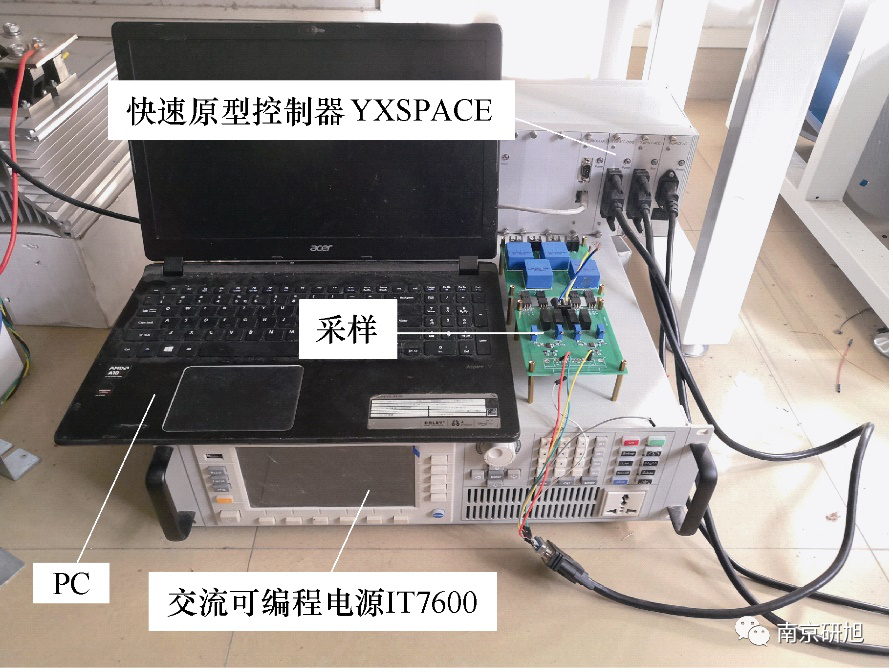

在本次研究中,作者团队采用YXSPACE控制器将SIMULINK下离线仿真算法模型快速转换到实际控制器的控制算法,YXSPACE控制器加快了仿真到实物验证的效率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

,这个很好理解,很多东西原来都是直接用硬件电路搞出来,现在有可编程器件了,再利用软件来实现。传统的硬件

a[10]=[0],用观察窗口观察变量时,只有a[0]=0,其他值仍然是随机值。难道数组的初始化必须对每个元素分别赋值吗? 2.

电路大多数都用在分频倍频,频率合成,解码… 该电路利用VOC的锁定工作,有良好的特性及抗

(PLL)解决方案有多种尺寸和类型可供选择。 PLL以整数N或小数N形式提供同时根据带宽利用无源或有源环路滤波器。 能够最终靠3线串行接口对其进行快速编程同时提供非常低的杂散抑制和较小

信号源的任何应用的理想选择,并且利用微带或陶瓷谐振器拓扑结构可提供出色的相位噪声性能。测试仪器雷达系统SFS10500H-LF

的输出频率和锁定时间参数的测试,给出了具体的测试电路和测试方法。对于应用在大规模电路系统中的

(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制

第十七章IP核之PLL实验PLL的英文全称是Phase Locked Loop,即

是一种反馈电路,其作用是使得电路上的时钟和某一外部时钟的相位同步。PLL通过比较外部信号的相位和由压控晶振(VCXO)的相位来实现同步的,在比较的过程中,

,具有延时小、受频差、电压畸变影响小、可自动跟踪电源频率的特性。文中结论的正确性在于可靠提取频率低的信号,讨论

电流的实时检测 /

【RISC-V开放架构设计之道阅读体验】先睹为快-学习RISC-V的案头好书